Even though the MC3 is in its core a Motorola 68xx design it can use 65xx parts. The bus and timings are the same. I initially planed on building an I/O board around the

6321 PIA but ended up trying out the feature packed

6522 VIA instead. The 6522 is actually still being manufactured by

WDC! The 6522 is familiar to anyone working with the 6502 or MOS/Commodore machines. In general it's a souped up 6821 with two timers and a shift register. The 6522 consumes more address space than the 6821 but each register can be directly addressed, thus making it faster for certain tasks. It requires four address pins instead of only two but for me that's a perfect match since my I/O boards each have 4 address lines making it a 1:1 match.

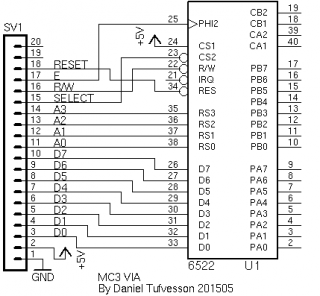

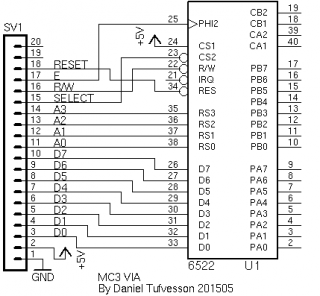

Connecting the 6522 to the MC3 20-pin I/O expansion bus require no extra circuitry. It's only a matter of connecting the corresponding pins together. Since there is no IRQ line on the I/O bus I will have to settle for polling the 6522.

Thank you Douglas Beattie for

sharing your Eagle 65xx library.

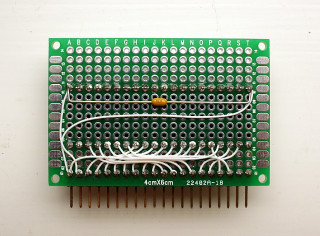

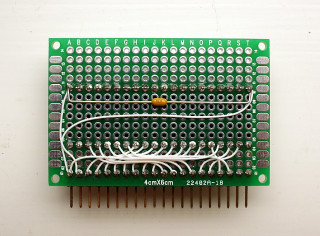

The 40-pin chip is a tight fit on the small 20-pin I/O board but it worked. For now there are no connectors for the 6522 ports.

Not much space left but I should be able to mount a suitable connector at the top of the board. I really like how the 6522 engineers have separated the bus pins and the I/O pins to different sides of the chip.

Inside the 6522

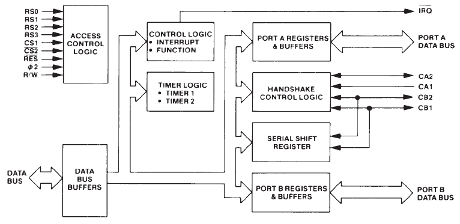

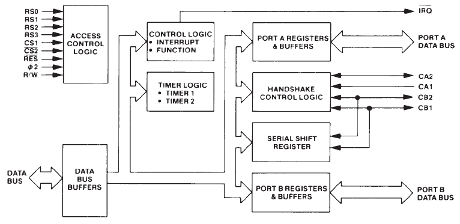

Above is the block diagram as seen in the G65SC22

datasheet. The 6522 has two 8-bit ports with two handshake lines each. Both ports are controlled by their corresponding data register and data direction register (just like the 6821 and many other designs based on the same concept). It also has two 16-bit timers and a shift register. Care must be taken to avoid the infamous

shift register bug happening in mode 011, external clocking of the shift register. The bug occurs when the shift register clock input falls at about the same time as the Φ2 clock falls, making the shift register lose one data bit. Very strange framing errors can occur when it happens. Garth Wilson has proposed a neat

solution for this that involves an external latch. Rumors has it that some variants of the 6522 does not suffer from this bug. I have a used the G65SC22 from CMD in my design that supposedly have this bug fixed. I need to set up a test to see if this is the case. In general, when dealing with the 6522 you have to assume all of them contains the bug in mode 011. The other shift register modes are unaffected as far as I know.

Connecting the 6522 to the MC3 20-pin I/O expansion bus require no extra circuitry. It's only a matter of connecting the corresponding pins together. Since there is no IRQ line on the I/O bus I will have to settle for polling the 6522.

Thank you Douglas Beattie for sharing your Eagle 65xx library.

Connecting the 6522 to the MC3 20-pin I/O expansion bus require no extra circuitry. It's only a matter of connecting the corresponding pins together. Since there is no IRQ line on the I/O bus I will have to settle for polling the 6522.

Thank you Douglas Beattie for sharing your Eagle 65xx library.

The 40-pin chip is a tight fit on the small 20-pin I/O board but it worked. For now there are no connectors for the 6522 ports.

The 40-pin chip is a tight fit on the small 20-pin I/O board but it worked. For now there are no connectors for the 6522 ports.

Not much space left but I should be able to mount a suitable connector at the top of the board. I really like how the 6522 engineers have separated the bus pins and the I/O pins to different sides of the chip.

Not much space left but I should be able to mount a suitable connector at the top of the board. I really like how the 6522 engineers have separated the bus pins and the I/O pins to different sides of the chip.

Above is the block diagram as seen in the G65SC22 datasheet. The 6522 has two 8-bit ports with two handshake lines each. Both ports are controlled by their corresponding data register and data direction register (just like the 6821 and many other designs based on the same concept). It also has two 16-bit timers and a shift register. Care must be taken to avoid the infamous shift register bug happening in mode 011, external clocking of the shift register. The bug occurs when the shift register clock input falls at about the same time as the Φ2 clock falls, making the shift register lose one data bit. Very strange framing errors can occur when it happens. Garth Wilson has proposed a neat solution for this that involves an external latch. Rumors has it that some variants of the 6522 does not suffer from this bug. I have a used the G65SC22 from CMD in my design that supposedly have this bug fixed. I need to set up a test to see if this is the case. In general, when dealing with the 6522 you have to assume all of them contains the bug in mode 011. The other shift register modes are unaffected as far as I know.

Above is the block diagram as seen in the G65SC22 datasheet. The 6522 has two 8-bit ports with two handshake lines each. Both ports are controlled by their corresponding data register and data direction register (just like the 6821 and many other designs based on the same concept). It also has two 16-bit timers and a shift register. Care must be taken to avoid the infamous shift register bug happening in mode 011, external clocking of the shift register. The bug occurs when the shift register clock input falls at about the same time as the Φ2 clock falls, making the shift register lose one data bit. Very strange framing errors can occur when it happens. Garth Wilson has proposed a neat solution for this that involves an external latch. Rumors has it that some variants of the 6522 does not suffer from this bug. I have a used the G65SC22 from CMD in my design that supposedly have this bug fixed. I need to set up a test to see if this is the case. In general, when dealing with the 6522 you have to assume all of them contains the bug in mode 011. The other shift register modes are unaffected as far as I know.